晶振,在板子上看上去一个不起眼的小器件,但是在数字电路里,就像是整个电路的心脏。数字电路的所有工作都离不开时钟,晶振的好坏,晶振电路设计的好坏,会影响到整个系统的稳定性。所以更多的了解晶振,选择好系统使用的晶振,对数字电路来说是决定成败的第一步。

我们目前常说的晶振都是石英晶体振荡器或者石英晶体谐振器的简称。他们都是利用石英晶体的压电效应制作而成。在石英晶体的两个电极上施加电场会使晶体产生机械变形,反之,如果在晶体两侧施加机械压力就会在晶体上产生电场。并且,这两种现象是可逆的。利用这种特性,在晶体的两侧施加交变电压,晶片就会产生机械振动,同时产生交变电场。这种震动和电场一般都很小,但是在某个特定频率下,振幅会明显加大,这就是压电谐振,和我们常见到的LC回路谐振有些类似。

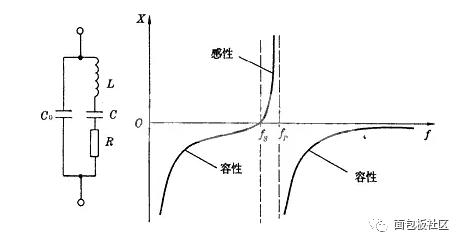

下图是晶振的电气等效电路和电抗频率特性曲线图:

从图中可以看出,当LCR这个支路发生串联谐振的时候,其串联谐振频率为fs,其计算公式和普通的串联谐振计算公式一样:

当频率继续提高,高于fs时,LCR支路呈感性,这样和C0产生并联谐振,并联谐振频率fp,其计算公式为:

其中由于晶振的特性,C远小于C0,所以fp和fs的值非常接近。通过电抗频率特性曲线图可以看出来,在这个狭窄的频率范围内,晶振整体表现出感性,这样只需要在晶振外部并联合适的电容,就可以组成并联谐振电路。然后把这个并联谐振电路加到负反馈电路中就可以构成正弦波振荡电路。这个合适的电容就是晶振的负载电容。

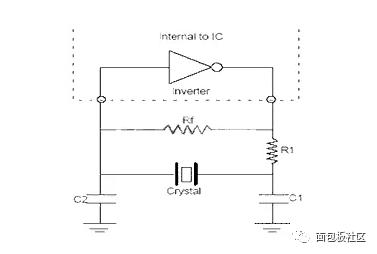

上图就是一个常见的晶振振荡电路,晶振和C1、C2组成并联谐振回路,接到芯片的管脚上,芯片内部的反相放大器和Rf组成负反馈回路,R1用来限制流入晶振的电流。有些芯片会把Rf和R1集成到器件中,这样就降低了电路设计的难度。,并且保证了系统的稳定性。晶振的重要参数就是负载电容,选择与负载电容相等的电容并联,能保证晶振工作在额定频率。假如晶振的负载电容是15pf,那么C1、C2我们可以选择30pf,考虑到芯片管脚电容和PCB走线电容的影响,这个取值也可以适当减小,27pf,22pf一般也能正常工作。在满足起震要求的情况下,C1、C2可以选择的尽量小,这样可以加快晶振的起震时间。需要注意的是,有些晶振厂商会直接提供C1、C2的推荐值,而不是给出负载电容,所以在实际使用的时候还是要根据使用的具体型号去和厂家确认。

晶振除了压电效应以外,还有一个不能被忽略的特性,就是温漂。晶振的振荡频率会随着环境温度的变化发生微小的偏移,这是晶振固有的特性。正是由于温漂的存在,普通晶振的精度很难做的很高,常见的晶振精度多为40ppm,20ppm,很难做到10ppm以下。这种精度在一些对晶振精度要求不高的场合,如微处理器的时钟输入等,完全能够满足需求。但是在无线通信,蜂窝应用,广播电视等应用领域,需要时钟精确同步,普通晶振就很难满足系统需求了。为了解决温漂带来的影响,系统就要选择精度更高的温补晶振或者恒温晶振。温补晶振是通过感应环境温度,然后将温度信息转换成控制量控制晶振的输出频率。现在的温补晶振多采用数字化技术,能够达到更精确的控制。而恒温晶振更进一步,将晶体置于恒温槽内,通过设置恒温工作点,使恒温槽保持一个恒温的状态,晶体在恒温槽内就可以不受外界温度的影响,大大提高晶振输出频率的稳定度。温补晶振和恒温晶振的输出精度都能够达到1ppm甚至更高。能够满足严苛的系统需求。

由于晶振在数字电路中的重要性,在使用和设计的时候我们需要小心处理:

a. 晶振内部存在石英晶体,所以在受到外部撞击或者跌落的时候容易造成石英晶体断裂破损造成晶振失效。在设计的时候就要考虑晶振的可靠安装以及位置尽量不要靠近板边,设备外壳等等。

b. 在手工焊接或者机器焊接的时候要注意焊接温度,晶振对温度比较敏感,焊接时温度不能过高,并且加热时间尽量短。

c. 设计的时候尽量缩短晶振部分的走线,晶振走线和其他信号线之间保留尽量远的距离,并且推荐将晶振的外壳接地,这些措施都能更好的避免干扰。

d. 谨慎选择C1、C2的容值。尽量按照厂家提供的推荐值设计。在满足起震要求的前提下,C1、C2的取值可以尽量小,能缩短晶振起震时间。

e. 注意晶振是否被过驱动,过驱动会影响晶振使用寿命。如果用示波器测试发现晶振的输出被削波,波峰波谷被削平,那么就要考虑晶振是否被过驱动。可以适当调整R1限流电阻的阻值。直到输出完整的正弦波。

—END—

热门推荐:

内容合作 | 视频、课程合作 | 开发板合作| 转载开白

请联系小助手微信:15889572951(微信同号)

点击阅读原文,下载《电路设计技术与技巧》

点击阅读原文,下载《电路设计技术与技巧》

长按二维码识别关注我们