жң¬ж–ҮжқҘжәҗ硬件еҚҒдёҮдёӘдёәд»Җд№Ҳ

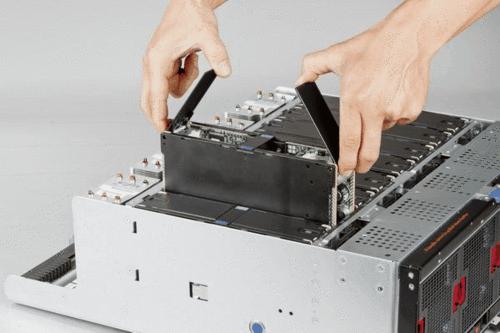

1гҖҒ зғӯжҸ’жӢ”жҰӮиҝ°

1.1еҺҶеҸІ

зғӯжҸ’жӢ”пјҲhot-pluggingжҲ–Hot SwapпјүеҚіеёҰз”өжҸ’жӢ”пјҢжҳҜжҢҮе°Ҷи®ҫеӨҮжқҝеҚЎжҲ–жЁЎеқ—зӯүеёҰз”өжҺҘе…ҘжҲ–移еҮәжӯЈеңЁе·ҘдҪңзҡ„зі»з»ҹпјҢиҖҢдёҚеҪұе“Қзі»з»ҹе·ҘдҪңзҡ„жҠҖжңҜгҖӮжҲ‘们ж—ҘеёёжңҖеёёз”Ёзҡ„еә”з”Ёе°ұжҳҜUSBзғӯжҸ’жӢ”гҖӮ

дёҖж–№йқўпјҢеңЁеҶӣдәӢгҖҒз”өдҝЎгҖҒйҮ‘иһҚзӯүйўҶеҹҹпјҢи®ҫеӨҮжҠ•е…ҘиҝҗиЎҢеҗҺпјҢеҝ…йЎ»еӨңд»Ҙ继ж—Ҙең°иҝҗиҪ¬пјҢеҜ№иҝҷдәӣи®ҫеӨҮзҡ„йғЁд»¶иҝӣиЎҢжӢҶиЈ…з»ҙдҝ®гҖҒз»ҙжҠӨгҖҒжү©еұ•ж—¶пјҢзі»з»ҹдёҚиғҪеҒңжңәпјҢеҒңжңәеҲҷж„Ҹе‘ізқҖйҮҚеӨ§зҡ„з»ҸжөҺжҚҹеӨұгҖӮиҝҷе°ұиҰҒжұӮи®ҫеӨҮйғЁд»¶иғҪеӨҹеңЁзі»з»ҹеёҰз”өиҝҗиЎҢзҡ„жғ…еҶөдёӢиҝӣиЎҢжҺҘе…ҘжҲ–иҖ…移еҮәгҖӮ

еҸҰдёҖж–№йқўпјҢеҜ№иҝһжҺҘеҲ°жҖ»зәҝдёҠзҡ„и®ҫеӨҮпјҢеҜ№еҚ•дёӘи®ҫеӨҮиҝӣиЎҢжҸ’е…ҘжҲ–иҖ…жӢ”еҮәзҡ„ж—¶еҖҷпјҢдёҚиғҪеҜ№жҖ»зәҝдә§з”ҹиҫғеӨ§е№Іжү°пјҢеҗҰеҲҷдјҡеңЁжҖ»зәҝдёҠдә§з”ҹиҫғеӨ§зҡ„еҷӘеЈ°пјҢеј•иө·жҖ»зәҝдёҠе…¶д»–и®ҫеӨҮзҡ„еҒңжңәжҲ–иҖ…иҜҜз Ғдә§з”ҹпјҢеҪұе“Қж•ҙжқЎжҖ»зәҝдёҡеҠЎгҖӮзғӯжҸ’жӢ”жҠҖжңҜжӯЈжҳҜеңЁиҝҷз§ҚйңҖжұӮдёӢеә”иҝҗиҖҢз”ҹгҖӮ

ж°‘з”ЁзғӯжҸ’жӢ”жҠҖжңҜејҖе§ӢдәҺPCжңәзҡ„ејҖеҸ‘дёӯпјҢд»Һ586ж—¶д»ЈејҖе§ӢпјҢзі»з»ҹжҖ»зәҝйғҪеўһеҠ дәҶеӨ–йғЁжҖ»зәҝзҡ„жү©еұ•пјҢжӯӨж—¶зҡ„зі»з»ҹжҖ»зәҝе·Із»ҸеҲқжӯҘж»Ўи¶ізғӯжҸ’жӢ”зҡ„иҰҒжұӮгҖӮ1997е№ҙејҖе§ӢпјҢж–°зҡ„BIOSдёӯеўһеҠ дәҶеҚіжҸ’еҚіз”ЁеҠҹиғҪзҡ„ж”ҜжҢҒпјҢиҷҪ然иҝҷз§ҚеҚіжҸ’еҚіз”Ёзҡ„ж”ҜжҢҒ并дёҚд»ЈиЎЁе®Ңе…Ёзҡ„зғӯжҸ’жӢ”ж”ҜжҢҒпјҢд»…ж”ҜжҢҒзғӯж·»еҠ е’ҢзғӯжӣҝжҚўгҖӮ

1.2 зғӯжҸ’жӢ”йҳІжҠӨзӯүзә§

жҢүз…§з”өи·ҜеёҰз”өжҸ’жӢ”ж—¶еҜ№еҷЁд»¶е’ҢдҝЎеҸ·зҡ„еҪұе“ҚзЁӢеәҰпјҢжҠҠеёҰз”өжҸ’жӢ”зҡ„йҳІжҠӨи®ҫи®ЎеҲҶдёәеӣӣдёӘзӯүзә§гҖӮд»Ӣз»ҚеҰӮдёӢгҖӮдҪҶиҜҘеӣӣдёӘзӯүзә§жҳҜж №жҚ®жҷ®йҖҡйҖ»иҫ‘еҷЁд»¶пјҲеҰӮй©ұеҠЁеҷЁзӯүпјүзҡ„з”өи·Ҝз»“жһ„жқҘе®ҡд№үзҡ„пјҢFPGAгҖҒCPLDзӯүеӨ§йҖ»иҫ‘еҷЁд»¶зҡ„з«ҜеҸЈз»“жһ„дёҺжҷ®йҖҡйҖ»иҫ‘еҷЁд»¶жңүиҫғеӨ§зҡ„еҢәеҲ«пјҢз»“жһ„жӣҙеҠ еӨҚжқӮпјҢдҪҶд»ҚеҸҜд»Ҙзӯүж•Ҳдёәжҷ®йҖҡйҖ»иҫ‘еҷЁд»¶зҡ„зғӯжҸ’жӢ”зӯүзә§гҖӮ

1пјү0зә§йҳІжҠӨ

е…·жңү0зә§йҳІжҠӨи®ҫи®Ўзҡ„з”өи·Ҝжқҝеә”еңЁе…Ҳе…іж–ӯдё»з”өжәҗзҡ„жғ…еҶөдёӢжүҚиғҪе®үе…Ёзҡ„еёҰз”өжҸ’жӢ”гҖӮе®ғжІЎжңүеҜ№зһ¬еҸҳз”өжөҒжҲ–зӘҒеҸҳз”өеҺӢзҡ„жҠ‘еҲ¶дҝқжҠӨпјҢжҸ’жӢ”иҝҮзЁӢдёӯжҸ’е…Ҙз”өи·ҜжқҝжҺҘеҸЈд№ҹдёҚиғҪиҝӣе…Ҙй«ҳйҳ»зҠ¶жҖҒгҖӮеҰӮжһңжҸ’е…Ҙз”өи·ҜжқҝеңЁзі»з»ҹжІЎжңүж–ӯз”өжғ…еҶөдёӢе°ұиҝӣиЎҢеёҰз”өжҸ’жӢ”пјҢжқҝдёҠзҡ„жҺҘеҸЈеҷЁд»¶жҲ–е…¶д»–е…ғ件еҫҲеҸҜиғҪеҸ—еҲ°жҚҹеқҸгҖӮеҸӘиғҪиҫҫеҲ°0зә§йҳІжҠӨи®ҫи®Ўзҡ„з”өи·ҜжқҝдёҚиғҪеёҰз”өжҸ’жӢ”гҖӮ

2пјү1зә§йҳІжҠӨпјҲPartial Power Downпјү

е…·жңү1зә§йҳІжҠӨи®ҫи®Ўзҡ„з”өи·ҜжқҝеңЁж–ӯз”өж—¶иғҪйҷҗеҲ¶еёҰз”өжҖ»зәҝе’ҢжҸ’е…Ҙз”өи·ҜжқҝжҺҘеҸЈд№Ӣй—ҙзҡ„з”өжөҒпјҢд»ҺиҖҢйҳІжӯўжҸ’е…Ҙз”өи·ҜжқҝеҸ—еҲ°жҚҹеқҸгҖӮиҝҷз§Қзһ¬жҖҒз”өжөҒйҷҗеҲ¶е°ұиғҪдҝқиҜҒеңЁдёҚжү“ж–ӯдё»з”өжәҗжғ…еҶөдёӢеёҰз”өжҸ’жӢ”з”өи·ҜжқҝпјҢдҪҶжҳҜеңЁеёҰз”өжҸ’жӢ”жңҹй—ҙпјҢдё»зі»з»ҹеҝ…йЎ»жҡӮеҒңдҝЎеҸ·дј иҫ“гҖӮиҝҷз§ҚйҳІжҠӨи®ҫи®ЎйңҖиҰҒдҪҝз”ЁIOFFз”өи·ҜгҖӮ

3пјү2зә§йҳІжҠӨпјҲHot Insertionпјү

е…·жңү2зә§йҳІжҠӨи®ҫи®Ўзҡ„з”өи·Ҝжқҝе…·жңүеёҰз”өжҸ’жӢ”жҖ§иғҪпјҢе®ғиғҪйҳІжӯўжҸ’е…Ҙз”өи·ҜжқҝжҸ’жӢ”ж—¶зҡ„й©ұеҠЁеҶІзӘҒгҖӮ2зә§йҳІжҠӨи®ҫи®ЎйҷӨдәҶе…·жңү1зә§йҳІжҠӨи®ҫи®Ўзҡ„иғҪеҠӣеӨ–пјҢдҝЎеҸ·з«ҜиҝҳиғҪеңЁз”өжәҗз”өеҺӢдёҠеҚҮеҲ°жҢҮе®ҡеҖјд№ӢеүҚдҝқжҢҒй«ҳйҳ»зҠ¶жҖҒпјҢеңЁз”өжәҗз”өеҺӢи¶…иҝҮиҝҷдёӘжҢҮе®ҡеҖјеҗҺдјҡжҢүз…§и®ҫзҪ®зҠ¶жҖҒиҫ“еҮәгҖӮз”өи·Ҝжқҝж–ӯз”өж—¶пјҢеңЁз”өжәҗз”өеҺӢдёӢйҷҚеҲ°йў„е®ҡз”өеҺӢеҖјд№ӢеүҚиҫ“еҮәдҝқжҢҒдёәй©ұеҠЁйҖ»иҫ‘з”өе№іпјҢ然еҗҺеҸҳжҲҗй«ҳйҳ»зҠ¶жҖҒгҖӮжҢүз…§2зә§йҳІжҠӨи®ҫи®Ўзҡ„иҰҒжұӮпјҢз”өи·ҜжқҝеёҰз”өжҸ’жӢ”жңҹй—ҙжҖ»зәҝдёҠзҡ„ж•°жҚ®дј иҫ“еҸҜиғҪдјҡиў«жү“ж–ӯгҖӮ2зә§йҳІжҠӨи®ҫи®Ўж—ўйңҖиҰҒ1зә§йҳІжҠӨи®ҫи®Ўдёӯзҡ„IOFFз”өи·ҜпјҢд№ҹйңҖиҰҒдёҠз”ө3жҖҒз”өи·ҜпјҲPU3SпјүгҖӮ

4пјү3зә§йҳІжҠӨпјҲLive Insertionпјү

е…·жңү3зә§йҳІжҠӨи®ҫи®Ўзҡ„з”өи·ҜжқҝеңЁеёҰз”өжҸ’жӢ”ж—¶еҜ№зі»з»ҹз”өжәҗе’ҢдҝЎеҸ·жІЎжңүе…¶д»–зҡ„йҷҗеҲ¶гҖҒзәҰжқҹе’ҢиҰҒжұӮгҖӮеёҰз”өжҸ’жӢ”е’Ңж•°жҚ®дәӨжҚўеҸҜеҗҢжӯҘиҝӣиЎҢпјҢеҚіеңЁд»»дҪ•жғ…еҶөдёӢиҝӣиЎҢжҸ’гҖҒжӢ”ж“ҚдҪңйғҪдёҚдјҡз ҙеқҸж•°жҚ®пјҢеҪ“然жӣҙдёҚдјҡжҚҹеқҸеҷЁд»¶гҖӮдёәдәҶиҫҫеҲ°иҝҷдәӣиҰҒжұӮпјҢ3зә§йҳІжҠӨи®ҫи®ЎеҗҢж—¶йңҖиҰҒIOFFгҖҒPU3Sе’Ңйў„е……з”өI/OгҖӮ

1.3 зғӯжҸ’жӢ”дјҡеҜјиҮҙзҡ„й—®йўҳ

еңЁд»ҘеүҚпјҢжҲ‘们дҪҝз”Ёз”өи„‘жҲ–иҖ…е…¶д»–з”өеӯҗи®ҫеӨҮж—¶пјҢжҖ»дјҡеҸ—еҲ°иӯҰе‘ҠпјҡдёҚиғҪеёҰз”өжҸ’жӢ”пјҢеҰӮжһңжҲ‘们еёҰз”өжҸ’жӢ”пјҢиҪ»еҲҷйҖ жҲҗзі»з»ҹжӯ»жңәжҲ–иҖ…йҮҚеҗҜпјҢйҮҚеҲҷйҖ жҲҗжҺҘеҸЈз”өи·Ҝ硬件жҚҹеқҸпјҢйҖ жҲҗе·ЁеӨ§жҚҹеӨұгҖӮиҝҷжҳҜд»Җд№ҲеҺҹеӣ е‘ўпјҢеҜ№дёҚж”ҜжҢҒзғӯжҸ’жӢ”зҡ„зі»з»ҹпјҢеёҰз”өжҸ’жӢ”дёәд»Җд№ҲдјҡйҖ жҲҗеҰӮжӯӨдёҘйҮҚзҡ„еҗҺжһңпјҹ

пјҲ1пјү зғӯжҸ’жӢ”еј•еҸ‘й—©й”Ғж•Ҳеә”пјҡзғӯжҸ’жӢ”еүҚи®ҫеӨҮд№Ӣй—ҙеҸҜиғҪеӯҳеңЁиҫғй«ҳз”өдҪҚе·®пјҢеҰӮжһңдёҚйҮҮеҸ–зӣёеә”жҺӘж–Ҫиҝҷз§Қз”өдҪҚе·®е°ҶеҜ№и®ҫеӨҮдёҠзҡ„IC иҠҜзүҮжһ„жҲҗдёҘйҮҚеҚұе®іпјҢе°Өе…¶жҳҜCMOSеҷЁд»¶пјҢжңүеҸҜиғҪеј•еҸ‘й—©й”Ғж•Ҳеә”гҖӮ

пјҲ2пјүзғӯжҸ’жӢ”иҜұеҸ‘йқҷз”өй—®йўҳпјҡиҷҪ然еҶ·жҸ’жӢ”иҝҮзЁӢдёӯд№ҹжңүйқҷз”өй—®йўҳпјҢдҪҶжҳҜз”ұдәҺзғӯжҸ’жӢ”ж—¶дёҖйғЁеҲҶз”өи·ҜжҳҜеӨ„дәҺдёҠз”өе·ҘдҪңзҠ¶жҖҒпјҢеӣ жӯӨзғӯжҸ’жӢ”ж—¶зҡ„йқҷз”өе№Іжү°дјҡеј•еҸ‘иҜёеҰӮвҖңй—©й”Ғж•Ҳеә”вҖқд№Ӣзұ»жҒ¶жҖ§ж•…йҡңпјҢйҷӨжӯӨд№ӢеӨ–пјҢзғӯжҸ’жӢ”еҜ№дәҺзЁіе®ҡе·ҘдҪңзҡ„иғҢжқҝи®ҫеӨҮзҡ„йқҷз”өе№Іжү°дҪҝеҫ—жң¬жқҘеңЁи®ҫеӨҮеҶ…йғЁзҡ„иғҢжқҝиҝһжҺҘеҷЁеҸҳжҲҗдәҶиў«йқҷз”өзӣҙжҺҘеҮ»дёӯзҡ„еӨ–йғЁжҺҘеҸЈгҖӮ

пјҲ3пјүзғӯжҸ’жӢ”еҜјиҮҙжөӘж¶Ңй—®йўҳпјҡеҪ“еҚ•жқҝжҸ’е…ҘжңәжЎҶж—¶пјҢжңәжЎҶдёӯе…¶д»–и®ҫеӨҮе·ІеӨ„дәҺзЁіе®ҡе·ҘдҪңзҠ¶жҖҒпјҢжүҖжңүеӮЁиғҪз”өе®№еқҮиў«е……ж»Ўз”өпјҢиҖҢеҚ•жқҝдёҠзҡ„з”өе®№жІЎжңүз”өиҚ·пјҢеҪ“и®ҫеӨҮдёҺдё»жқҝжҺҘи§Ұж—¶и®ҫеӨҮдёҠзҡ„з”өе®№е……з”өе°ҶеңЁзҹӯж—¶й—ҙеҶ…д»Һз”өжәҗзі»з»ҹеҗёе…ҘеӨ§йҮҸз”өиғҪпјҢеңЁдҫӣз”өзәҝи·ҜдёҠеҪўжҲҗдёҖиӮЎжҜ”жӯЈеёёе·ҘдҪңз”өжөҒй«ҳеҮәж•°еҖҚзҡ„жөӘж¶Ңз”өжөҒгҖӮжөӘж¶Ңз”өжөҒдјҡдҪҝз”өжәҗеҮәзҺ°зһ¬ж—¶и·ҢиҗҪеҜјиҮҙзі»з»ҹеӨҚдҪҚгҖҒеј•еҸ‘й—©й”Ғж•Ҳеә”гҖҒеҜјиҮҙиҝһжҺҘеҷЁз”өи·ҜжқҝйҮ‘еұһиҝһзәҝе’Ңз”өи·Ҝе…ғ件зғ§еқҸгҖӮ

пјҲ4пјүзғӯжҸ’жӢ”еҜ№жҖ»зәҝйҖ жҲҗе№Іжү°пјҡжҖ»зәҝдёҠжҸ’е…ҘжқҝеҚЎж—¶пјҢз”ұдәҺж–°жҸ’е…ҘжқҝеҚЎз”өе®№зҡ„е……з”өд»ҘеҸҠдёҠз”өиҝҮзЁӢдёӯдёҖдәӣдҪҺйҳ»жҠ—йҖҡйҒ“зҡ„еӯҳеңЁпјҢдјҡдә§з”ҹжһҒеӨ§зҡ„жөӘж¶Ңз”өжөҒпјҢжӢүдҪҺжҖ»зәҝз”өе№іпјҢеҜ№жҖ»зәҝдёҠе…¶д»–и®ҫеӨҮдә§з”ҹе№Іжү°пјҢеҪұе“ҚжҖ»зәҝдёҠе…¶д»–и®ҫеӨҮзҡ„жӯЈеёёиҝҗиЎҢгҖӮеҗҢж—¶жҸ’жӢ”ж—¶д№ҹеҜ№жҖ»зәҝжҺҘеҸЈеёҰжқҘйқҷз”өй—®йўҳгҖӮ

2гҖҒзғӯжҸ’жӢ”еҜјиҮҙзҡ„й—©й”Ғж•Ҳеә”еҸҠе…¶йҳІжІ»

2.1 й—©й”Ғж•Ҳеә”еҸҠе…¶жңәзҗҶ

пјҲ1пјү е®ҡд№үпјҡй—©й”ҒпјҲLatch upпјүжҳҜжҢҮCMOSеҷЁд»¶жүҖеӣәжңүзҡ„еҜ„з”ҹеҸҢжһҒжҷ¶дҪ“з®Ўиў«и§ҰеҸ‘еҜјйҖҡпјҢеңЁз”өжәҗе’Ңең°д№Ӣй—ҙеҪўжҲҗдёҖдёӘдҪҺйҳ»йҖҡи·ҜгҖӮ

пјҲ2пјүж•…йҡңзҺ°иұЎпјҡCMOSиҠҜзүҮзҡ„з”өжәҗе’Ңең°д№Ӣй—ҙеӨ§з”өжөҒйҖҡиҝҮпјҢеҜјиҮҙиҠҜзүҮиҮӘиә«зғ§жҜҒеӨұж•ҲпјҢдёҘйҮҚж—¶дјҡжіўеҸҠе‘Ёеӣҙзҡ„з”өи·Ҝе’Ңжҳ“зҮғеҷЁд»¶пјҲеҰӮпјҡй’Ҫз”өе®№пјүгҖӮ

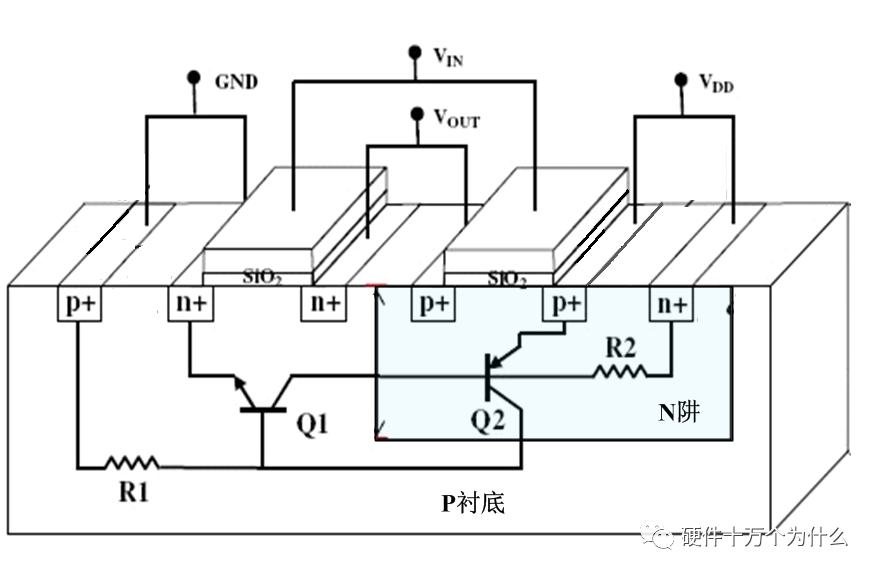

пјҲ3пјүеҶ…йғЁжңәзҗҶпјҡи§Ғеӣҫ2-1

еӣҫ2-1 й—©й”ҒеҶ…йғЁжңәзҗҶзӨәж„Ҹеӣҫ

еҰӮеӣҫ2-1жүҖзӨәпјҢCMOSеҸ‘з”ҹй—©й”Ғж•Ҳеә”ж—¶пјҢе…¶дёӯзҡ„NMOSзҡ„жңүжәҗеҢәгҖҒPиЎ¬еә•гҖҒNйҳұгҖҒPMOSзҡ„жңүжәҗеҢәжһ„жҲҗдёҖдёӘn-p-n-pзҡ„з»“жһ„пјҢеҚіеҜ„з”ҹжҷ¶дҪ“з®ЎпјҲQ1гҖҒQ2пјүпјҢжң¬иҙЁжҳҜеҜ„з”ҹзҡ„дёӨдёӘеҸҢжһҒжҷ¶дҪ“з®Ўзҡ„иҝһжҺҘгҖӮPиЎ¬жҳҜNPNзҡ„еҹәжһҒпјҢд№ҹжҳҜPNPзҡ„йӣҶз”өжһҒпјҢд№ҹе°ұжҳҜNPNзҡ„еҹәжһҒе’ҢPNPзҡ„йӣҶз”өжһҒжҳҜиҝһзқҖзҡ„пјӣNйҳұж—ўжҳҜPNPзҡ„еҹәжһҒпјҢд№ҹжҳҜNPNзҡ„йӣҶз”өжһҒгҖӮеҶҚеӣ дёәPиЎ¬еә•е’ҢNйҳұеёҰжңүдёҖе®ҡзҡ„з”өйҳ»пјҢеҲҶеҲ«з”ЁR1е’ҢR2жқҘиЎЁзӨәгҖӮ

еҪ“NйҳұжҲ–иҖ…иЎ¬еә•дёҠзҡ„з”өжөҒи¶іеӨҹеӨ§пјҢдҪҝеҫ—R1жҲ–R2дёҠзҡ„еҺӢйҷҚдёә0.7VпјҢе°ұдјҡжҳҜQ1жҲ–иҖ…Q2ејҖеҗҜгҖӮдҫӢеҰӮQ1ејҖеҗҜпјҢе®ғдјҡжҸҗдҫӣи¶іеӨҹеӨ§зҡ„з”өжөҒз»ҷR2пјҢдҪҝеҫ—R2дёҠзҡ„еҺӢйҷҚд№ҹиҫҫеҲ°0.7VпјҢиҝҷж ·R2д№ҹдјҡејҖеҗҜпјҢеҗҢж—¶пјҢеҸҲеҸҚйҰҲз”өжөҒжҸҗдҫӣз»ҷQ1пјҢеҪўжҲҗжҒ¶жҖ§еҫӘзҺҜпјҢжңҖеҗҺеҜјиҮҙеӨ§йғЁеҲҶзҡ„з”өжөҒд»ҺVDDзӣҙжҺҘйҖҡиҝҮеҜ„з”ҹжҷ¶дҪ“з®ЎеҲ°GNDпјҢиҖҢдёҚжҳҜйҖҡиҝҮMOSFETзҡ„жІҹйҒ“пјҢиҝҷж ·ж …еҺӢе°ұдёҚиғҪжҺ§еҲ¶з”өжөҒгҖӮ

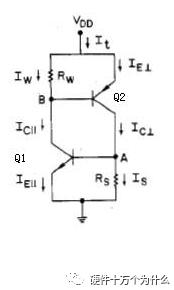

пјҲ4пјүй—©й”ҒжңәзҗҶзҡ„йӣҶжҖ»еҷЁд»¶иЎЁиҝ°пјҡ

е…ғеҷЁд»¶дёӯзҡ„еҜ„з”ҹжҷ¶дҪ“з®ЎиҝһжҺҘе…ізі»еҸҜд»Ҙз”ЁйӣҶжҖ»е…ғ件жқҘиЎЁзӨәпјҢеҰӮеӣҫ2-2жүҖзӨәпјҢе…¶з»“жһ„е®һйҷ…дёҠжҳҜдёҖдёӘеҸҢз«ҜPNPNз»“з»“жһ„пјҢеҰӮжһңеҶҚеҠ дёҠжҺ§еҲ¶ж …жһҒпјҢе°ұз»„жҲҗй—ЁжһҒи§ҰеҸ‘зҡ„й—ёжөҒз®ЎгҖӮиҜҘз»“жһ„е…·жңүеҰӮеӣҫ3жүҖзӨәзҡ„иҙҹйҳ»зү№жҖ§пјҢиҜҘзҺ°иұЎе°ұз§°дёәй—©й”Ғж•Ҳеә”пјҲй—©й”Ғжң¬жҳҜй—ёжөҒз®Ўзҡ„дё“жңүеҗҚиҜҚпјүгҖӮеҚіеҸҢз«ҜPNPNз»“еңЁжӯЈеҗ‘еҒҸзҪ®жқЎд»¶дёӢпјҢеҷЁд»¶ејҖе§ӢеӨ„дәҺжӯЈеҗ‘йҳ»ж–ӯзҠ¶жҖҒпјҢеҪ“з”өеҺӢиҫҫеҲ°иҪ¬жҠҳз”өеҺӢж—¶пјҢеҷЁд»¶дјҡз»ҸиҝҮиҙҹйҳ»еҢәз”ұйҳ»ж–ӯзҠ¶жҖҒиҝӣе…ҘеҜјйҖҡзҠ¶жҖҒпјҺиҝҷз§ҚзҠ¶жҖҒзҡ„иҪ¬жҚўпјҢеҸҜд»Ҙз”ұз”өеҺӢи§ҰеҸ‘(=0)пјҢд№ҹеҸҜд»Ҙз”ұй—ЁжһҒз”өжөҒи§ҰеҸ‘(вү O)гҖӮй—ЁжһҒи§ҰеҸ‘еӨ§еӨ§йҷҚдҪҺдәҶжӯЈеҗ‘иҪ¬жҠҳз”өеҺӢгҖӮ

еӣҫ2 -2PNPNеҸҢз«ҜеҷЁд»¶

дёӨдёӘеҜ„з”ҹжҷ¶дҪ“з®Ўе·ҘдҪңж—¶пјҢеҪўжҲҗжӯЈеҸҚйҰҲз”өи·ҜпјҢеҠ ж·ұеҸҜжҺ§зЎ…еҜјйҖҡпјҢйҖ жҲҗзҡ„з»“жһңеңЁеҷЁд»¶зә§зҡ„жҸҸиҝ°дёҖж ·пјҢдёҖиӮЎеӨ§зҡ„з”өжөҒе°Ҷз”ұз”өжәҗжөҒеҗ‘жҺҘең°з«ҜпјҢеҜјиҮҙдёҖиҲ¬жӯЈеёёз”өи·Ҝе·ҘдҪңдёӯж–ӯпјҢз”ҡиҮідјҡз”ұдәҺй«ҳз”өжөҒж•Јзғӯзҡ„й—®йўҳиҖҢзғ§жҜҒиҠҜзүҮ

2.2 й—©й”Ғзҡ„дә§з”ҹжқЎд»¶

пјҲ1пјүеӯҳеңЁжӯЈеҸҚйҰҲпјҡеҜ„з”ҹеҸҢжһҒжһҒжҷ¶дҪ“з®Ўеӣһи·Ҝз”өжөҒеўһзӣҠеҝ…йЎ»еӨ§дәҺ1гҖӮОІ1ОІ2.>1

пјҲ2пјүеӨ–и§ҰеҸ‘жқЎд»¶пјҡдёҖдёӘз»ҙжҢҒи¶іеӨҹй•ҝж—¶й—ҙзҡ„еӨ–йғЁз”өжөҒпјҢдҪҝеҸҢжһҒеһӢжҷ¶дҪ“з®ЎеҜјйҖҡиө·жқҘгҖӮ

пјҲ3пјүз”өжөҒдҫӣеә”иғҪеҠӣпјҡеӨ–з”өи·ҜиғҪжҢҒз»ӯжҸҗдҫӣз»ҙжҢҒй—©й”ҒжүҖеҝ…йЎ»зҡ„з”өжөҒгҖӮ

2.3 й—©й”Ғзҡ„еёёи§ҒиҜұеҸ‘еҺҹеӣ

пјҲ1пјүиҫ“е…Ҙ/иҫ“еҮәи„ҡз”өеҺӢпјҡй«ҳз”өе№іжҜ”иҠҜзүҮз”өжәҗиҝҳй«ҳпјҢдҪҺз”өе№іжҜ”иҠҜзүҮең°иҝҳдҪҺпјҢиҝҷжҳҜжңҖеёёи§Ғзҡ„иҜұеҸ‘еҺҹеӣ гҖӮ

пјҲ2пјүз”өжәҗз«ҜејӮеёёзҡ„жөӘж¶Ңз”өеҺӢжҲ–еҷӘеЈ°е№Іжү°пјҢ

пјҲ3пјүең°зәҝеј•е…ҘејӮеёёе№Іжү°з”өеҺӢгҖӮ

2.4зғӯжҸ’жӢ”иҜұеҸ‘й—©й”Ғзҡ„еҺҹеӣ еҲҶжһҗ

пјҲ1пјүйҖҡи®Ҝз®Ўи„ҡе…ҲдәҺз”өжәҗз®Ўи„ҡжҺҘйҖҡеҜјиҮҙCMOSеҷЁд»¶зҡ„иҫ“е…Ҙ/иҫ“еҮәи„ҡз”өеҺӢй«ҳдәҺз”өжәҗз”өеҺӢжҲ–дҪҺдәҺең°з”өеҺӢгҖӮ

пјҲ2пјүжқҝеҚЎжҸ’е…Ҙзһ¬й—ҙз”ұдәҺз”өе®№е……з”өз”өжөҒпјҢеҜјиҮҙиғҢжқҝз”өжәҗејӮеёёжіўеҠЁпјҢеј•еҸ‘еҷЁд»¶й—©й”ҒгҖӮ

пјҲ3пјүеҚ•жқҝжҸ’е…Ҙж—¶жқҝдёҠйқҷз”өж”ҫз”өеҜјиҮҙзҡ„й—©й”Ғ

пјҲ4пјүжқҝеҚЎжӢ”еҮәзһ¬й—ҙз”ұдәҺз”өж„ҹзҡ„ж„ҹз”ҹз”өеҺӢеҜјиҮҙиғҢжқҝCMOSеҷЁд»¶й—©й”ҒгҖӮ

2.5й—©й”Ғзҡ„йў„йҳІжҺӘж–Ҫ

пјҲ1пјү з”өи·ҜжҺҘеҸЈйғЁеҲҶйҮҮз”ЁйҳІжҠӨжҺӘж–ҪпјҡйҳІжӯўи§ҰеҸ‘дҝЎеҸ·зҡ„еј•е…ҘгҖӮ

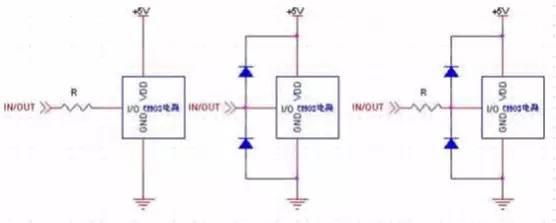

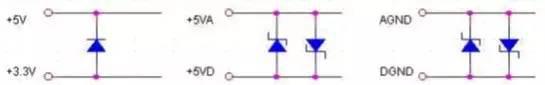

пјҲ2пјүCOMSеҷЁд»¶иҫ“е…Ҙ/иҫ“еҮәз«ҜеҠ йҷҗжөҒз”өйҳ»гҖӮй©ұеҠЁй•ҝзәҝиҙҹиҪҪж—¶пјҢеҒҡеҘҪеҢ№й…ҚпјҢд»ҘеҮҸе°ҸиҝҮеҶІгҖҒдёӢеҶІпјҢе…Ғи®ёзҡ„жқЎд»¶дёӢпјҢеҸҜеңЁCMOSеҷЁд»¶з«ҜеҸЈеӨ„еҠ дёӨдёӘдәҢжһҒз®ЎпјҢдёҖдёӘжҺҘең°пјҢдёҖдёӘжҺҘз”өжәҗгҖӮзі»з»ҹе…·жңүз”ЁжҲ·еҸҜж“ҚдҪңзҡ„I/OпјҢеңЁI/OдёІжҺҘдёҖдёӘз”өйҳ»йҷҗжөҒпјҢ并еҸҜеңЁз«ҜеҸЈеӨ„еҠ дёӨдёӘдәҢжһҒз®ЎпјҢдёҖдёӘжҺҘең°пјҢдёҖдёӘжҺҘз”өжәҗгҖӮ

пјҲ3пјүе°ҸеҠҹиҖ—еҷЁд»¶з”өжәҗзәҝдёҠдёІйҷҗжөҒз”өйҳ»пјҢз”өжәҗдёІз”өйҳ»пјҢйҷҗжөҒпјҢж¶ҲйҷӨй—©й”ҒеҜјиҮҙеҷЁд»¶зҡ„жҚҹеқҸгҖӮ

пјҲ4пјүйҳІжӯўз”өжәҗ/ең°зәҝз”өеҺӢжіўеҠЁ

пјҲ5пјүйҒҝе…ҚеӨ§з”өе®№иҙҹиҪҪ

пјҲ6пјүеёҰз”өжҸ’жӢ”ж—¶пјҢиҰҒжұӮиҝһжҺҘйЎәеәҸдёәпјҡGNDгҖҒдҪҺз”өеҺӢз”өжәҗгҖҒй«ҳз”өеҺӢз”өжәҗгҖҒI/OгҖӮе…¶дёӯз”өеҺӢд»Ҙз»қеҜ№еҖји®ЎгҖӮзӣёеҗҢе№…еҖјзҡ„жӯЈиҙҹз”өжәҗеҗҢж—¶дёҠз”өпјҢеҸҜдҪҝдёӨиҖ…зҡ„еҪұе“Қзӣёдә’жҠөж¶ҲгҖӮ

пјҲ7пјүеҒҡеҘҪз”өжәҗеҺ»иҖҰпјҢйҒҝе…ҚдёҠз”өж—¶жҲ–е·ҘдҪңдёӯпјҢз”өжәҗз”өеҺӢдёҠеҶІжҲ–дёӢеҶІеҜјиҮҙзҡ„й—©й”ҒгҖӮ

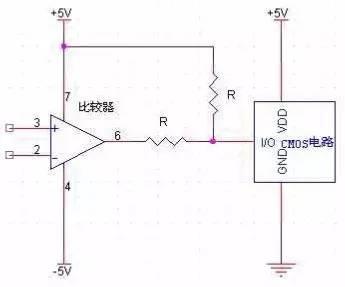

пјҲ8пјүж•°еӯ—з”өи·ҜдёҺжЁЎжӢҹз”өи·ҜзӣёжҺҘж—¶пјҢеҰӮдёӢеӣҫпјҢйҖҡиҝҮз”өйҳ»еҲҶеҺӢжҜ”з”ЁдәҢжһҒз®Ўз®қдҪҚж•ҲжһңиҰҒеҘҪгҖӮ

пјҲ9пјү继з”өеҷЁзӯүж„ҹжҖ§иҙҹиҪҪпјҢеҠ еҸҚжҺҘдәҢжһҒз®Ўеҗёж”¶жөӘж¶Ңз”өжөҒгҖӮ

пјҲ11пјүй«ҳдҪҺз”өеҺӢз”өжәҗд№Ӣй—ҙжҺҘдәҢжһҒз®ЎпјҢйҒҝе…ҚеңЁдёҠдёӢз”өж—¶пјҢдҪҺз”өеҺӢз”өжәҗз«Ҝз”өеҺӢи¶…иҝҮй«ҳз”өеҺӢз”өжәҗз«ҜиҝҮеӨҡпјҢиө·з®қдҪҚдҪңз”ЁгҖӮ

пјҲ12пјүеҗҢз”өеҺӢзҡ„дёҚеҗҢз”өжәҗд№Ӣй—ҙеҠ дёӨдёӘзӣёдә’еҸҚжҺҘзҡ„иӮ–зү№еҹәдәҢжһҒз®ЎгҖӮ

пјҲ13пјүAGNDдёҺDGNDд№Ӣй—ҙеҠ дёӨдёӘзӣёдә’еҸҚжҺҘзҡ„иӮ–зү№еҹәдәҢжһҒз®ЎгҖӮ

дёӢйӣҶеҶ…е®№йў„е‘Ҡпјҡ

зғӯжҸ’жӢ”еҜјиҮҙзҡ„йқҷз”өй—®йўҳеҸҠе…¶йҳІжІ»

зғӯжҸ’жӢ”еҜјиҮҙзҡ„жөӘж¶Ңй—®йўҳеҸҠе…¶йҳІжІ»

жҖ»зәҝзғӯжҸ’жӢ”

зғӯжҸ’жӢ”жңҖж–°и§ЈеҶіж–№жЎҲ

жң¬ж–Үж•ҙзҗҶиҮӘ

1гҖҒгҖҠе·ҘзЁӢжҠҖжңҜеҹәзЎҖ-зғӯжҸ’жӢ”зҹҘиҜҶиҜҰи§ЈеҸҠжЎҲдҫӢеҲҶжһҗж•ҷжқҗгҖӢзҷҫеәҰж–Үеә“пјҢдҪңиҖ…дёҚиҜҰ

2гҖҒ

3гҖҒKyechongKim a, Agis A. Iliadis пјҢLatch-upeffects in CMOS inverters due to high power pulsed electromagnetic interference

4гҖҒ GENDA.HU,ABetter Understand of CMOS Latch-Up

й•ҝжҢүдәҢз»ҙз ҒиҜҶеҲ«е…іжіЁжҲ‘们