1гҖҒи¶…з»“еҠҹзҺҮMOSFETиҫ“еҮәз”өе®№иҝҹж»һж•Ҳеә”

й«ҳйў‘й«ҳеҠҹзҺҮеҜҶеәҰејҖе…із”өжәҗдёәдәҶжҸҗй«ҳж•ҲзҺҮпјҢйҖҡеёёдҪҝз”Ёйӣ¶з”өеҺӢZVSиҪҜејҖе…іжҠҖжңҜгҖӮеҠҹзҺҮMOSFETејҖйҖҡеүҚпјҢCOSSз”өеҺӢVDSдёәзӣҙжөҒжҜҚзәҝз”өеҺӢпјҢCOSSз”өе®№еӮЁеӯҳиғҪйҮҸпјҢйҖҡиҝҮеӨ–еҠ з”өж„ҹLе’ҢCOSSдёІиҒ”жҲ–并иҒ”пјҢеҪўжҲҗLCи°җжҢҜз”өи·ҜпјҢCOSSж”ҫз”өпјҢVDSи°җжҢҜдёӢйҷҚпјӣеҪ“VDSи°җжҢҜдёӢйҷҚеҲ°0ж—¶пјҢеҠҹзҺҮMOSFETеҶ…йғЁеҸҚ并иҒ”еҜ„з”ҹдәҢжһҒз®ЎиҮӘ然еҜјйҖҡз»ӯжөҒпјҢVDSз”өеҺӢеҮ д№Һдёә0пјҢжӯӨж—¶пјҢејҖйҖҡеҠҹзҺҮMOSFETпјҢе°ұеҸҜд»Ҙе®һзҺ°йӣ¶з”өеҺӢZVSејҖйҖҡгҖӮ

еҠҹзҺҮMOSFETе…іж–ӯж—¶пјҢзӣҙжөҒжҜҚзәҝз”өеҺӢеҜ№COSSз”өе®№е……з”өпјҢVDSз”өеҺӢд»Һ0ејҖе§ӢдёҠеҚҮпјӣз”ұдәҺи¶…з»“еҠҹзҺҮCOSSз”өе®№йқһзәҝжҖ§зү№жҖ§пјҢеңЁз”өеҺӢдёә0ж—¶COSSи¶іеӨҹеӨ§пјҢVDSз”өеҺӢдёҠеҚҮйҖҹеәҰйқһеёёж…ўпјҢdV/dTдёҠеҚҮж–ңзҺҮйқһеёёе°ҸгҖӮеҠҹзҺҮMOSFETе…іж–ӯеҗҺпјҢIDз”өжөҒд»ҺжңҖеӨ§еҖјдёӢйҷҚеҲ°0иҝҮзЁӢдёӯпјҢVDSе’ҢIDз”өжөҒзҡ„дәӨеҸ еҢәйқўз§ҜеҫҲе°ҸпјҢе…іж–ӯжҚҹиҖ—йқһеёёе°ҸпјҢиҮӘ然еҪўжҲҗйӣ¶з”өеҺӢZVSе…іж–ӯгҖӮ

зҗҶи®әдёҠпјҢZVSиҪҜејҖе…іиҝҮзЁӢдёӯпјҢCOSSз”өе®№е……ж”ҫз”өпјҢеҹәжң¬дёҠжІЎжңүжҚҹиҖ—гҖӮе®һйҷ…еә”з”ЁдёӯеҚҙеҸ‘зҺ°пјҢеҠҹзҺҮMOSFETеңЁZVSиҪҜејҖе…іиҝҮзЁӢдёӯпјҢCOSSз”өе®№е……ж”ҫз”өиҝҮзЁӢеӯҳеңЁдёҖе®ҡзҡ„йўқеӨ–жҚҹиҖ—пјҢж— жі•жҒўеӨҚеӯҳеӮЁеңЁиҫ“еҮәз”өе®№COSSдёӯзҡ„е…ЁйғЁиғҪйҮҸпјҢиҝҷдёӘзҺ°иұЎз§°дёәи¶…з»“еҠҹзҺҮMOSFETиҫ“еҮәз”өе®№зҡ„иҝҹж»һпјҲж»һжҙ„пјүж•Ҳеә”пјҢе…¶жңҖе…Ҳз”ұзҫҺеӣҪEnphaseе…¬еҸёе·ҘзЁӢеёҲеҸ‘зҺ°пјҡ

Coss Related Energy Loss in Power MOSFETs Used in Zero Voltage Switched Applications, J. B. Fedison, M. Fornage, M. J. Harrison, D. R. Zimmanck, Enphase Energy Inc., APEC 2014.

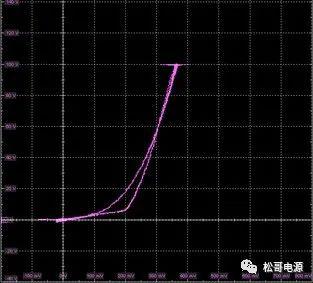

еӣҫ1 ж–ҮзҢ®дёӯзҡ„жіўеҪў

2гҖҒи¶…з»“еҠҹзҺҮMOSFETиҫ“еҮәз”өе®№зҡ„иҝҹж»һж•Ҳеә”жөӢйҮҸ

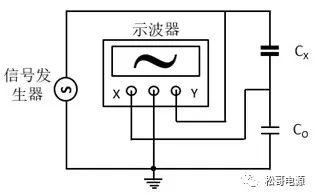

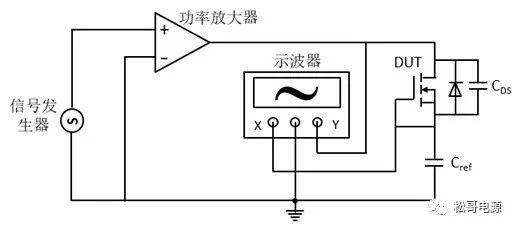

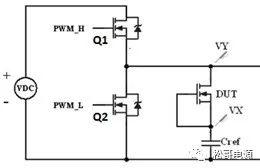

дәӢе®һдёҠпјҢеҫҲеӨҡйҷ¶з“·з”өе®№д№ҹе…·жңүз”өиҝҹж»һж•Ҳеә”пјҢжөӢйҮҸз”өиҝҹж»һеӣһзәҝеә”з”ЁжңҖе№ҝжіӣзҡ„ж–№жі•жҳҜSawyer-Towerжі•пјҢеҰӮеӣҫ1жүҖзӨәгҖӮе…¶дёӯпјҢCx дёәеҫ…жөӢйҮҸзҡ„з”өе®№пјҢCoдёәж ҮеҮҶз”өе®№пјҢйҖҡеёёпјҢCoзҡ„з”өе®№еҖјиҝңеӨ§дәҺCxгҖӮ

еӣҫ2 Sawyer-Towerжі•

и¶…з»“еҠҹзҺҮMOSFETиҫ“еҮәз”өе®№иҝҹж»һеӣһзәҝзҡ„жөӢйҮҸз”өи·Ҝе’Ңйҷ¶з“·з”өе®№зҡ„жөӢйҮҸз”өи·Ҝзұ»дјјпјҢеҰӮеӣҫ2жүҖзӨәгҖӮе…¶дёӯпјҢMOSFETж …жһҒGе’ҢжәҗжһҒSиҝһжҺҘеңЁдёҖиө·пјҢе…¶иҫ“еҮәз”өе®№дёәCOSSпјҢCref дёәж ҮеҮҶз”өе®№пјҢCrefзҡ„з”өе®№еҖјиҝңеӨ§дәҺCOSSпјҢеӣ жӯӨпјҢMOSFETзҡ„VDSз”өеҺӢдёәпјҡ

е…¶дёӯпјҢVYдёәзӨәжіўеҷЁYиҪҙпјҲYйҖҡйҒ“пјүзҡ„з”өеҺӢпјҢVXдёәзӨәжіўеҷЁXиҪҙпјҲXйҖҡйҒ“пјүзҡ„з”өеҺӢгҖӮ

еӣҫ3 жөӢйҮҸи¶…з»“еҠҹзҺҮMOSFETиҫ“еҮәз”өе®№иҝҹж»һеӣһзәҝ

MOSFETзҡ„Qossдёәпјҡ

Crefз”өе®№зҡ„з”өеҺӢдёәVXпјҢCOSSе’ҢCrefдёІиҒ”пјҢдәҢиҖ…з”өжөҒдёҖж ·пјҢе……гҖҒж”ҫз”өж—¶й—ҙе’Ңз”өжөҒдёҖж ·пјҢеӣ жӯӨпјҢе®ғ们еӮЁеӯҳзҡ„з”өиҚ·д№ҹзӣёеҗҢпјҡ

жүҖд»Ҙпјҡ

(a) ж–№жіўжіўеҪўдә§з”ҹз”өи·Ҝ

(b) ж–№жіўжіўеҪўеӣҫ

еӣҫ4 жөӢйҮҸзҡ„дҝЎеҸ·жіўеҪўдә§з”ҹз”өи·Ҝ

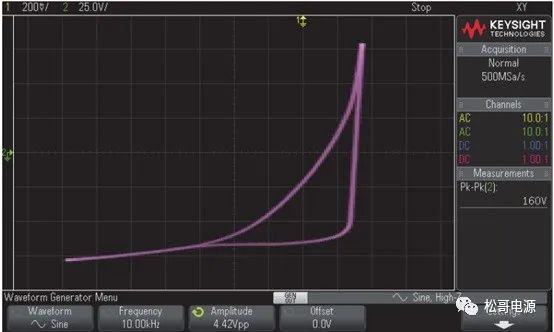

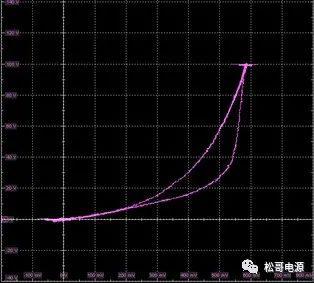

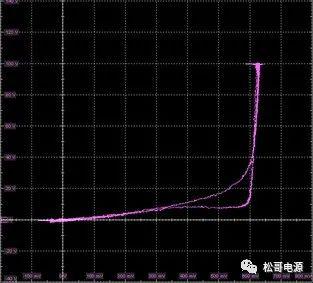

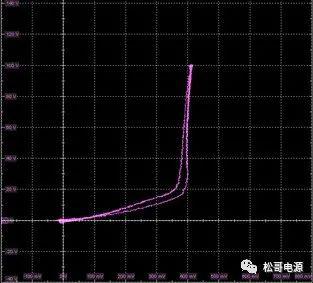

е°ҶзӨәжіўеҷЁжөӢйҮҸзҡ„дҝЎеҸ·Xе’ҢYпјҢй…ҚзҪ®жҲҗY-YжЁЎејҸпјҢе°ұеҸҜд»Ҙеҫ—еҲ°и¶…з»“еҠҹзҺҮMOSFETиҫ“еҮәз”өе®№зҡ„з”өеҺӢе’Ңз”өиҚ·зҡ„иҝҹж»һеӣһзәҝпјҢеҰӮеӣҫ5жүҖзӨәгҖӮеӣҫ5дёӯпјҢзәөиҪҙYиҪҙдёәз”өеҺӢVDSпјҢжөӢйҮҸдәҶ4дёӘдёҚеҗҢеһӢеҸ·и¶…з»“еҠҹзҺҮMOSFETиҫ“еҮәз”өе®№иҝҹж»һеӣһзәҝгҖӮ

(a) еҷЁд»¶A1

(b) еҷЁд»¶I2

пјҲcпјү еҷЁд»¶A3

пјҲdпјү еҷЁд»¶A4

еӣҫ5 дёҚеҗҢеһӢеҸ·зҡ„и¶…з»“еҠҹзҺҮMOSFETиҫ“еҮәз”өе®№иҝҹж»һеӣһзәҝ

3гҖҒи¶…з»“еҠҹзҺҮMOSFETиҫ“еҮәз”өе®№иҝҹж»һж•Ҳеә”дә§з”ҹеҺҹеӣ

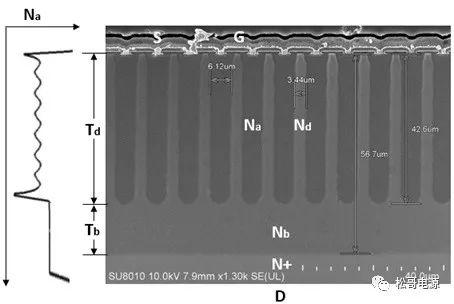

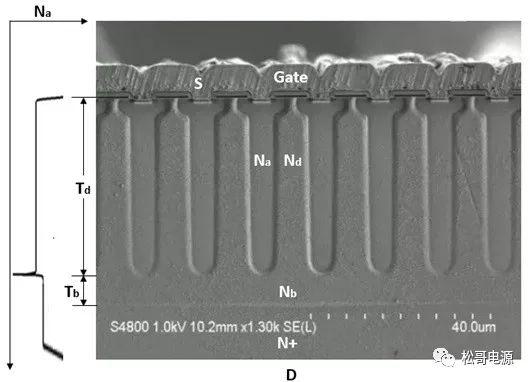

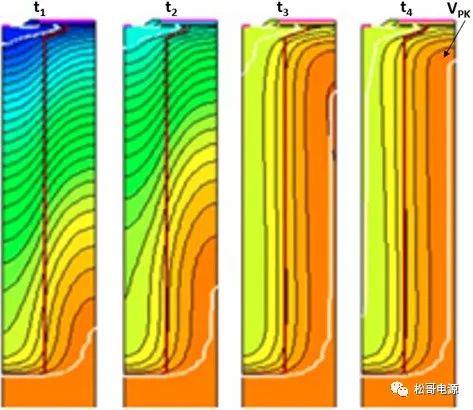

и¶…з»“еҠҹзҺҮMOSFETжҠҖжңҜзӣ®еүҚйҮҮеҸ–еӨҡеұӮеӨ–延е’Ңж·ұжІҹж§Ҫе·ҘиүәпјҢзӣёеҜ№дәҺе№ійқўз»“жһ„пјҢPйҳұдёӢ移еҪўжҲҗPжҹұз»“жһ„пјҢеҰӮеӣҫ6гҖҒеӣҫ7жүҖзӨәгҖӮйҖҡеёёжғ…еҶөпјҢи¶…з»“еҠҹзҺҮMOSFETзҡ„COSSеңЁе……з”өиҝҮзЁӢдёӯпјҢи¶…з»“NжҹұгҖҒPжҹұжңҖеҲқзҡ„移еҠЁиҪҪжөҒеӯҗпјҢдјҡеңЁж”ҫз”өиҝҮзЁӢдёӯе®Ңе…Ёж¶ҲиҖ—е°ҪгҖӮдҪҶжҳҜпјҢеҰӮжһңеңЁCOSSе……з”өйҳ¶ж®өпјҢдёҖдәӣ移еҠЁиҪҪжөҒеӯҗиў«йҡ”зҰ»ж»һз•ҷ,д№ҹе°ұжҳҜеҪўжҲҗж»һз•ҷз”өиҚ·(Stranded Charges QSTR)пјҢиҖ—е°ҪеұӮжү©еұ•дёҚдёҖиҮҙпјҢжІҝзқҖNжҹұгҖҒPжҹұеҪўжҲҗжІЎжңүиҖ—е°Ҫзҡ„еҫ®е°ҸеҢәеҹҹпјҢеҜјиҮҙе……з”өе’Ңж”ҫз”өиҝҮзЁӢдёҚдёҖиҮҙпјҢжңҖз»ҲеҪўжҲҗиҝҹж»һж•Ҳеә”пјҢд№ҹе°ұжҳҜCOSSе……ж”ҫз”өиҝҮзЁӢдёӯдёҖдәӣиғҪйҮҸеңЁеҶ…йғЁиў«ж¶ҲиҖ—гҖӮи¶…з»“еҠҹзҺҮMOSFETиҫ“еҮәз”өе®№иҝҹж»һж•Ҳеә”пјҢе’Ңж»һз•ҷз”өиҚ·зӣҙжҺҘзӣёе…ігҖӮ

еӣҫ6 еӨҡеұӮеӨ–延结жһ„Multiple Epi Structure

еӣҫ7 ж·ұжІҹж§Ҫз»“жһ„Trench Epi Structure

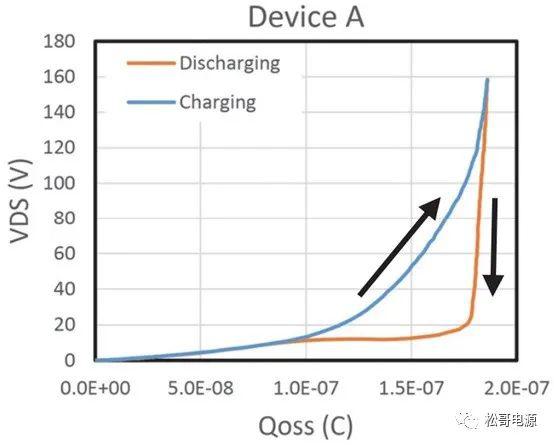

д»Һеӣҫ5еҸҜд»ҘеҸ‘зҺ°пјҢи¶…з»“еҠҹзҺҮMOSFETиҫ“еҮәз”өе®№зҡ„иҝҹж»һж•Ҳеә”пјҢдёҺе…¶жјҸжһҒжәҗжһҒжүҖеҠ з”өеҺӢVDSзӣҙжҺҘзӣёе…іпјҢиҝҷз§Қж•Ҳеә”еӨ§еӨҡеҸ‘з”ҹеңЁдҪҺеҺӢйҳ¶ж®өпјҢиҝҷд№ҹиЎЁжҳҺпјҢи¶…з»“еҠҹзҺҮMOSFETиҫ“еҮәз”өе®№зҡ„иҝҹж»һж•Ҳеә”е’Ңи¶…з»“жҹұзҠ¶з»“жһ„еңЁдҪҺдәҺ100VеҸ‘з”ҹзҡ„дёүз»ҙиҖ—е°Ҫжңүе…ігҖӮ

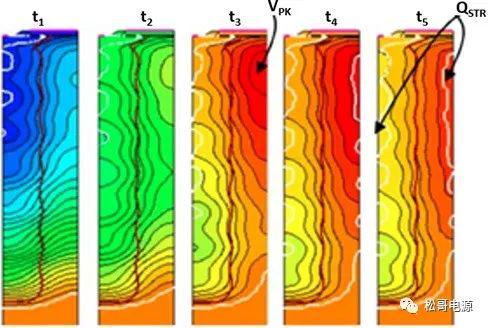

жӯӨеӨ–пјҢCOSSзҡ„иҝҹж»һж•Ҳеә”д№ҹе’Ңи¶…з»“еҠҹзҺҮMOSFETз»“жһ„зӣёе…іпјҢеҶ…йғЁжҷ¶иғһеҚ•е…ғе°әеҜёи¶Ҡе°ҸпјҢиҝҹж»һж•Ҳеә”и¶ҠжҳҺжҳҫгҖӮзӣёе…іж–ҮзҢ®з ”究表жҳҺпјҡж·ұжІҹж§Ҫз»“жһ„жІЎжңүж»һз•ҷз”өиҚ·QSTRж•Ҳеә”пјҢеӨҡеұӮеӨ–延结жһ„е…·жңүж»һз•ҷз”өиҚ·QSTRж•Ҳеә”пјҢеҰӮеӣҫ8гҖҒеӣҫ9жүҖзӨәгҖӮеӣҫ8е’Ңеӣҫ9дёӯпјҢеҲ—еҮәдәҶиҝҷз§Қз»“жһ„зҡ„д»ҝзңҹз”өеҠҝзәҝеҲҶеёғеӣҫPotential line distributionгҖӮеӨҡеұӮеӨ–延结жһ„еңЁеҠЁжҖҒиҖ—е°ҪиҝҮзЁӢдёӯпјҢж»һз•ҷз”өиҚ·QSTRпјҢеҮәзҺ°еңЁNжҹұе’ҢPжҹұзҡ„еә•йғЁе’ҢйЎ¶йғЁгҖӮ

Jaume Roig and Filip Bauwens, Origin of Anomalous COSS Hysteresis in Resonant Converters With Superjunction FETs

иҝҷиЎЁжҳҺпјҡеӨҡеұӮеӨ–延结жһ„MEMI(Multi implant multi epitaxy)зҡ„ж»һз•ҷз”өиҚ·QSTRж•Ҳеә”пјҢжҜ”ж·ұжІҹж§Ҫз»“жһ„TFET(Trench filling epitaxial growth)иҰҒдёҘйҮҚгҖӮ

еӣҫ8 ж·ұжІҹж§Ҫз»“жһ„Trench Epi Structure

еӣҫ9 еӨҡеұӮеӨ–延结жһ„Multiple Epi Structure

4гҖҒи¶…з»“еҠҹзҺҮMOSFETиҫ“еҮәз”өе®№иҝҹж»һж•Ҳеә”зҡ„еҠҹиҖ—жөӢйҮҸ

дёәдәҶеҫ—еҲ°и¶…з»“еҠҹзҺҮMOSFETиҫ“еҮәз”өе®№иҝҹж»һж•Ҳеә”жүҖдә§з”ҹзҡ„еҠҹиҖ—пјҢеҸҜд»Ҙз”Ёзӯүж•Ҳжі•жөӢйҮҸгҖӮдҪҝз”Ёеӣҫ3зҡ„з”өи·ҜпјҢеңЁдёҖе®ҡиҫ“е…Ҙз”өеҺӢгҖҒе·ҘдҪңйў‘зҺҮfsдёӢзЁіе®ҡе·ҘдҪңпјҢжөӢйҮҸи¶…з»“еҠҹзҺҮMOSFETеЈійЎ¶зҡ„жё©еҚҮО”TгҖӮ然еҗҺпјҢеңЁи¶…з»“еҠҹзҺҮMOSFETеҶ…йғЁеҜ„з”ҹдәҢжһҒз®ЎйҖҡиҝҮдёҖе®ҡз”өжөҒIFпјҢдҪҝи¶…з»“еҠҹзҺҮMOSFETеЈійЎ¶зҡ„жё©еҚҮеҗҢж ·иҫҫеҲ°О”TпјҢжөӢйҮҸеҜ„з”ҹдәҢжһҒз®ЎеҺӢйҷҚVFпјҢеҲҷеҸҜд»Ҙеҫ—еҲ°зӣёеә”жқЎд»¶дёӢпјҢиҫ“еҮәз”өе®№иҝҹж»һж•Ҳеә”жүҖдә§з”ҹзҡ„еҠҹиҖ—пјҡ

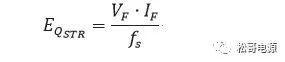

иҫ“еҮәз”өе®№иҝҹж»һж•Ҳеә”жүҖдә§з”ҹзҡ„иғҪйҮҸпјҡ