1.1 横向双扩散型场效应晶体管的结构

功率MOSFET即金属氧化物半导体场效应晶体管(Metal Oxide Semiconductor FieldEffect Transistor)有三个管脚,分别为栅极(Gate),漏极(Drain)和源极(Source)。功率MOSFET为电压型控制器件,驱动电路简单,驱动的功率小,而且开关速度快,具有高的工作频率。常用的MOSFET的结构有横向双扩散型场效应晶体管LDMOS(Lateral Double-Diffused MOS)、平面双扩散型场效应晶体管(Planar MOS)和沟槽双扩散型场效应晶体管(Trench MOS)。

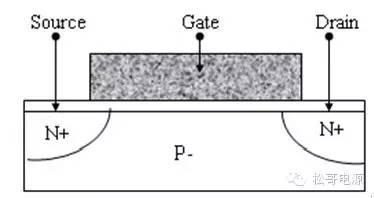

N沟道的横向双扩散型场效应晶体管的结构如图1所示,栅极,漏极和源极都在硅片的上表面,下部为衬底,当电流从漏极流向源极时,电流在硅片内部横向流动,而且主要从硅片的上表层流过,因此没有充分应用硅片的尺寸,电流和电压的额定值受到限制。但这种结构具有低的电容,因此开关速度快,主要适合低压应用,如微处理器、运放、数字电路及射频电路等。

图1:N沟道横向导电的平面结构

2 平面双扩散型场效应晶体管

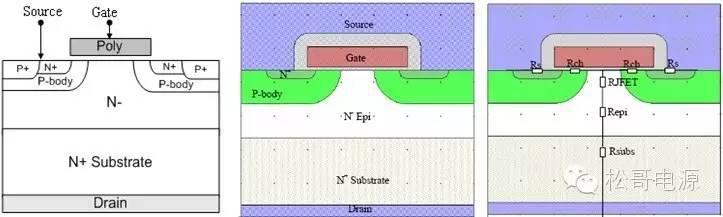

N沟道的平面双扩散型场效应晶体管的结构如图2所示,栅极和源极在硅片的上表面而漏极连接到衬底的下表面。源极和漏极在晶元的相对的平面,当电流从漏极流向源极时,电流在硅片内部垂直流动,因此可以充分的应用硅片的面积,来提高通过电流的能力,合适于功率MOSFET的应用。

这种结构称为垂直导电双扩散MOS结构VDMOSFET(Vertical Double Diffused MOSFET)。N沟道MOSFET衬底为高掺杂的N+衬底,高掺杂沟道部分的体电阻小。然后上面为为N-的epi层,上面有两个连续的扩散区P-,沟道在P-区形成。在P-区内部,扩散形成的N+为源极。硅片表面形成栅极氧化物,多晶硅栅极材料沉积后,在连接到栅极的多晶硅层下面,就会形成一个薄的高质量的氧化层,从而产生沟道。

工作原理是:栅极和源极间加正向电压,P-区中的少数载流子,即“少子”,也就是电子,被电场吸引到栅极下面的表面,随着栅极和源极正向偏置电压的增加,更多的电子被吸引到这个区域,这样本地的电子密度要大于空穴,从而出现“反转”,即在栅极下面的P-区的材料从P型变成N型,形成N型“沟道”,电流可以直接通过漏极的N+型区、N-型区、栅极下面N型沟道,流到源极N+型区。

在功率MOSFET的内部,由许多这样的单元,也称“晶胞”,并联而成。硅片的面积越大,所能加工的单元越多,器件的导通电阻越小,能够通过的电流就越大;同样,在单位的面积的硅片上,能够加工的晶胞越多,也就是晶胞单位密度越大,器件的导通电阻也就越小。通常器件的导通电阻越小,电流额定值也就越大。

由于栅极不通过功率主回路的大电流,因此栅极占用的部分硅片的面积不能充分得到应用,也就影响到能够加工的晶胞单位密度的最大值。同时,由于栅极的面积大,寄生电容就越大,因此开关性能较差。

这种结构工艺简单,单元的一致性较好,因此它的跨导的特性比较好,雪崩能量比较高,同时寄生电容也较大,主要应用于高压的功率MOSFET和开关频率不太高的中压功率MOSFET。

如果需要低的导通电阻,只有增大的晶片面积,晶片的面积受到封装尺寸的限制,因此不适合于一些高功率密度的应用。平面型高压的功率MOSFET管的耐压主要通过厚的低掺杂的N-的外延层即epi层来控制。

图2:N沟道垂直导电的平面结构及Rdson组成

在低压器件中,由于N-外延层比较薄,N+层和漏极的金属衬底对通态的电阻影响大;大于100V的器件,N-外延层是通态电阻主要组成部分。低压器件中,沟道电阻和晶元之间的区域也会对通态电阻产生影响。

沟道电阻主要依赖于栅极驱动程度。Vgs增加,Rdson减小。开始时,当Vgs增到阈值电压Vth以上时,Rdson很快降减小,表明MOSFET沟道导通。当Vgs进一步增加,Rdson下降比较来缓,因为沟道完全导通,MOSFET导通电阻由其它的电阻组成部分决定。

当器件缩小到更小的尺寸,RS , RCH也减小,因为更多的单个的单元晶胞将堆积在给定的硅片区。另一方面,P+区域夹在两个N区域之间,当电流被限制在靠近P-体区域的狭窄的N-区中流过时,将产生JFET效应,即把各晶胞的P-基区所夹住的那部分看为JFET,是结型场效应晶体管(Junction FET)的简称,产生一个寄生的JFET,结型场效应管是以PN结上的电场来控制所夹沟道中的电流,从而增加通态电阻。

平面MOSFET的RDS(ON)由于下面几个部分组成:

RS : 源极电阻

RCH : 沟道电阻

RJFET : JFET区电阻

REPI : 硅片顶层电阻,外延硅epi,epi控制着MOSFET可以承受的阻断电压的值

RSUBS : 硅衬底电阻,epi从它上面生长。

3 沟槽双扩散型场效应晶体管

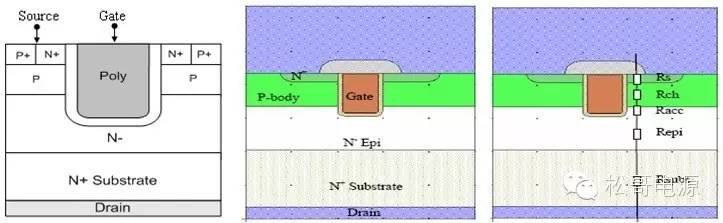

从图2的结构知道,对于单位面积的硅片,如果要减小功率MOSFET的导通电阻,就要提高晶胞单位密度,也就是要减小每个晶胞单元的尺寸,即要减小栅极的所占用的面积。如果采用图2的结构,用深度来换面积,将栅极埋入基体中,形成垂直的沟道,从而保持沟道的宽度,这样形成的结构称为垂直导电的沟槽结构。

图3:N沟道垂直导电的沟槽结构及Rdson组成

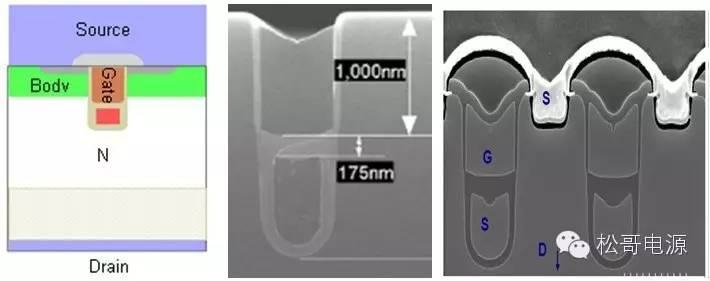

工作原理是:栅极和源极间加正向电压时,在P-和栅极相邻的区域,形成垂直的沟道,电流从漏极流向源极时,同样的,电流垂直流过硅片内部,可以看到,栅极的宽度远小于垂直导电的平面结构,因此具有更小的单元的尺寸,导通电阻更小。常用的沟槽有U型沟槽和V型沟槽,U型沟槽使用更多。

这种结构由于要开沟槽,工艺复杂,单元的一致性,跨导的特性和雪崩能量比垂直导电的平面结构稍差,但对于同样面积的硅片,它的导通电阻更高,寄生电容小,适合于低压的功率MOSFET,应用于高频非隔离的DCDC变换器,以提高系统的效率,降低系统的体积。AOS的AON6240就是采用这种技术,电压40V,Rdson=1.6m,广泛的应用于通讯模块电源的副边同步整流。

沟漕和平面型MOSFET的RDS(ON)组成部分主要的不同在于出现JFET部分,沟漕型由于没有JFET效应,可以得到更高密度的缩减,实现低的RDS(ON)。

沟漕MOSFET的RDS(ON)由于下面几个部分组成:

RS:源极电阻

RCH:沟道电阻,栅极下沟道的电阻。

RACC:聚集区电阻

REPI:硅片顶层的电阻,外延硅即epi层,在原始的低阻衬底(substrate)硅片上向外延伸一层高阻层,其控制着MOSFET可以承受的阻断电压值。

RSUBS: 硅衬底电阻,epi从它上面生长。

三种结构的导通电阻和Qgd关系如图4所示。

图4:三种结构的导通电阻和QGD关系

名词解释

JFET效应:在平面MOSFET沟道中,二边的P区中间夹着一个N区,由于二个P区在外面通过S极连在一起,因此,这个结构形成了标准的JFET结构。

4 隔离栅SGT场效应晶体管

功率MOSFET的导通电阻Rds(on)和寄生的电容是一个相互矛盾的参数,为了减小导通电阻,就必须增加硅片面积;硅片面积增加,寄生的电容也要增加,因此对于一定的面积硅片,只有采用新的工艺技术,才能减小的寄生的电容。通常功率MOSFET的开关损耗主要与米勒电容、即漏极和栅极的电容Qgd相关,如果减小漏极和栅极相对的接触面积就可以减小米勒电容,最为直观的方法就是分拆栅极并采用屏蔽技术SGT(SplitGate Technology)。

图5中,除了栅极结构,其它的部分就是标准的采用Trench工艺的功率MOSFET。栅极被分割成上下两个部分,下部分用一些特殊的材料屏蔽起来,下部分在内部和上部分的栅极相连,而下部分栅极的屏蔽层被连接到源极,从而减小漏极栅极米勒电容,极大的减小了开关过程中米勒平台的持续的时间,降低了开关损耗。

同时,这种结构由于改变了内部电场的形态,将传统的三角形电场进一步的变为更为压缩的梯形电场,可以进一步减小epi层的厚度,降低导通电阻,减小热阻。这种结构是AOS的专利技术,目前AOS新一代的低、中压的功率MOSFET,广泛的采用这种结构,如AON6262E/AO4262E,就是采用这种技术,专门针对手机快冲QC的副边同步整流SSR应用,DCM工作模式具有非常优异的效率,同时对于CCM模式具有优异EMI及抗ESD能力。

图5:采用SGT新型功率MOSFET结构

下周讲解主题:继续讨论高压超结型Super Junction功率MOSFET的结构及工作原理,就是COOL MOSFET所采用的结构,并详细分析如何实现低RDSON。

松哥电源(微信公众号:adlsong2016):探讨电源理论,分析电源应用,分享电源新思维!更多技术文章,请关注以下公众号

AOS产品,关注下面公从号